In VLSI design, OCV (On-Chip Variation), AOCV (Advanced On-Chip Variation), and POCV (Process On-Chip Variation) refer to methods and models used for accounting for variations in the manufacturing process that affect the performance of a chip. These variations are critical to ensure the robustness and performance of the chip under varying operating conditions and manufacturing tolerances.

Here’s a breakdown of each model:

1. OCV (On-Chip Variation)

OCV refers to variations that occur due to inconsistencies within the chip itself, which can be caused by factors like temperature, voltage fluctuations, or process variation during fabrication. OCV models account for these variations when performing timing analysis and static timing verification.

Key Features of OCV:

- Variation in device parameters (e.g., threshold voltage, channel length, and oxide thickness) due to process variations across the chip.

- Typically considers corner cases (e.g., best-case and worst-case conditions) where the chip’s speed may vary based on environmental or internal factors.

- OCV models are typically conservative and are used in the initial stages of chip design.

Applications:

- Static Timing Analysis (STA) under different process corners.

- Provides worst-case scenario estimations to ensure design robustness.

2. AOCV (Advanced On-Chip Variation)

AOCV is an advanced version of OCV that provides a more accurate representation of local variation across the chip. AOCV models account for spatial variations that are not considered in basic OCV models, allowing for more precise analysis of the chip’s performance.

Key Features of AOCV:

- Accounts for local variations in the process that can affect different parts of the chip differently.

- Provides more granular analysis than OCV by considering different cell types or regions of the chip.

- Uses statistical methods to model the variation across the chip, considering factors like distance between cells, temperature gradients, and power supply noise.

Applications:

- More accurate timing analysis for complex designs, especially in deep submicron technologies.

- Can be used for clock tree synthesis (CTS) to minimize clock skew due to local variations.

3. POCV (Process On-Chip Variation)

POCV focuses specifically on the variation introduced by the manufacturing process itself. It is a more detailed method for considering how process variations (such as differences in lithography, etching, doping, etc.) impact the overall chip.

Key Features of POCV:

- Focuses on process-induced variations such as those due to random dopant fluctuations, line edge roughness, and mask misalignment during fabrication.

- Statistical modeling is used to account for process variation over the entire chip, focusing on manufacturing issues.

- It enables designers to understand the effect of global process variations on chip performance and helps in yield prediction.

Applications:

- Yield analysis: Helps estimate the chip’s yield based on expected process variations.

- More detailed models are used for Signoff and final optimization of designs.

Key Differences between OCV, AOCV, and POCV:

| Model | Focus | Level of Detail | Applications |

|---|---|---|---|

| OCV | General on-chip variations (voltage, temperature, and process) | Basic, worst-case scenario | Timing analysis for conservative designs |

| AOCV | Local variation across the chip, including region-specific inconsistencies | More granular, regional variation | More accurate timing analysis for complex designs, deep-submicron technology |

| POCV | Process-induced variations during manufacturing (global process variations) | High-level, statistical process modeling | Yield estimation, signoff, process variability analysis |

Which Model to Use?

- OCV is generally used in earlier stages of the design process when a basic understanding of variation is sufficient.

- AOCV should be used for more advanced designs (especially in deep-submicron technologies) to accurately account for local variations and spatial effects.

- POCV is critical for understanding process variability, especially in terms of yield prediction and final Signoff.

OCV vs AOCV vs POCV with examples –

1. OCV (On-Chip Variation) Example in Timing Analysis

Scenario:

You’re designing a digital circuit (say, a microprocessor) with multiple flip-flops connected by long wires. You want to ensure that the signal reaches its destination within the required time for each flip-flop to capture it correctly.

Application of OCV:

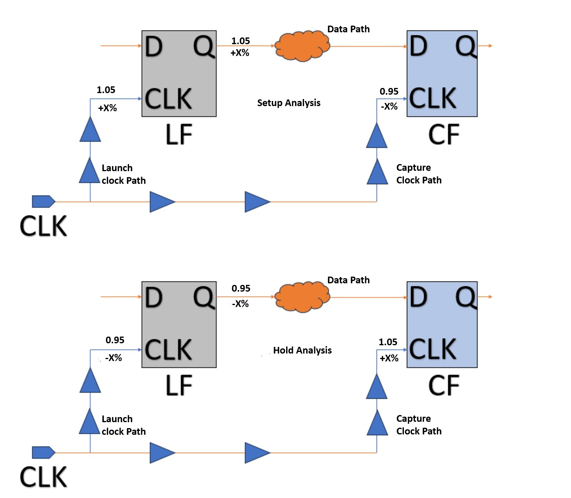

- In static timing analysis (STA), OCV is used to check if the timing paths meet the setup and hold time requirements. It assumes worst-case process variations across the chip, meaning it considers the best and worst-case scenarios for each component’s performance (e.g., slowest and fastest gates).

- For example, if the threshold voltage (Vth) is higher than expected, the gate delay increases. OCV considers this worst-case scenario where the delay is maximized, and it checks if the setup time (time required before the clock edge) and hold time (time required after the clock edge) are still met.

- Result: If any timing paths violate these constraints under the OCV model, the designer may need to adjust the clock period or make optimizations like pipelining or increasing drive strength.

2. AOCV (Advanced On-Chip Variation) Example in Timing Analysis

Scenario:

In the same microprocessor design, some regions of the chip are clocked faster than others, and temperature gradients across the chip may cause local variations in delay. For example, the delay of a logic gate near a power-hungry block (like an ALU) will be higher due to localized heating.

Application of AOCV:

- AOCV uses local variations to model how delays vary across different regions of the chip. For instance, the timing analysis tool considers that gates closer to high-power areas (e.g., the CPU cores) may have slower propagation delays because of temperature effects.

- AOCV breaks down the chip into regions and calculates timing margins for each region separately. It also considers voltage variation within these regions due to power delivery network (PDN) fluctuations.

- Result: The tool may show that a path between flip-flops in the region near the ALU does not meet timing due to localized process variation (e.g., increased resistance due to temperature). In this case, the designer might choose to optimize the clock tree or buffer insertion for this region to meet timing constraints.

3. POCV (Process On-Chip Variation) Example in Yield Estimation and Process Design

Scenario:

In an advanced SoC design, you’re using 7nm technology, and the fabrication process may introduce variability in transistor sizes (e.g., channel lengths or oxide thickness) due to lithography or etching imperfections. These variations impact the overall chip performance and yield.

Application of POCV:

- POCV considers global process variations that occur across the chip due to the manufacturing process. This includes variations in transistor parameters such as gate length, threshold voltage, and oxide thickness.

- Signoff tools using POCV models simulate the overall process variability to predict how the chip will perform under real-world conditions. For instance, the simulation will model random dopant fluctuations and line-edge roughness to predict which parts of the chip may be underperforming or failing due to these variations.

- Result: By using POCV, designers can predict whether certain parts of the chip may have lower yield due to process variations, and adjustments can be made. For example, a specific part of the design might need additional guard bands or layout optimizations (e.g., resizing critical transistors or optimizing routing layers) to increase the likelihood that the chip will function correctly after manufacturing.

Combined Usage in a Design Flow:

In a modern VLSI SoC design, OCV, AOCV, and POCV are used at different stages to ensure that the design is both robust and manufacturable:

- During Design & Synthesis (OCV): OCV is used in the early stages to make sure that timing paths are safe under worst-case conditions and to perform initial timing checks across the entire chip.

- During Detailed Timing Optimization (AOCV): Once the design becomes more complex and placement begins, AOCV is applied to identify region-specific issues, considering local process and environmental variations.

- During Final Signoff and Yield Analysis (POCV): After placement and routing, POCV is used for detailed signoff to assess how process variations may affect overall yield and performance, ensuring that the chip can be reliably manufactured.

Summary of Applications:

- OCV: Ensures design robustness under worst-case variations.

- AOCV: Provides more accurate, region-specific timing optimization.

- POCV: Helps estimate chip yield and predict manufacturing issues.