What is Scan in VLSI Design? Key Technique for Improved Testing

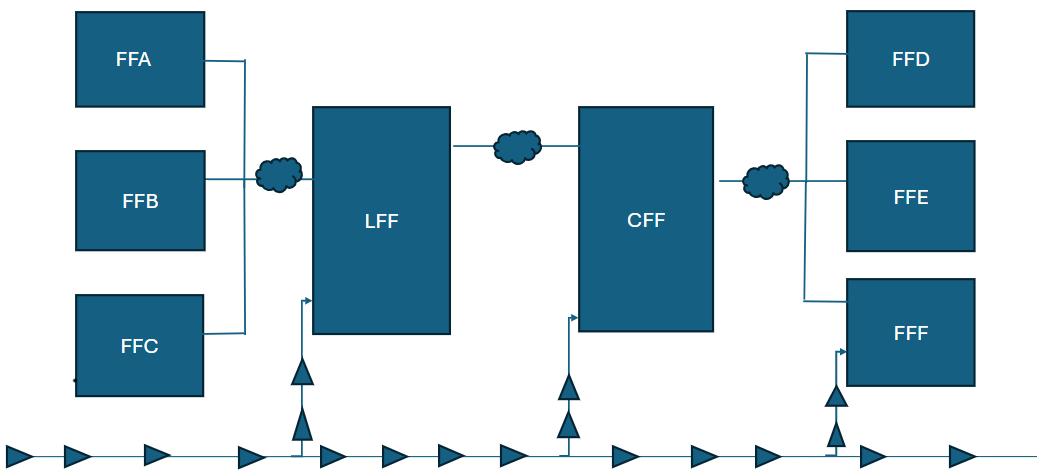

In VLSI (Very Large Scale Integration) design, scan is a technique used to facilitate testing and debugging of digital circuits by making it easier to observe and control the internal states of the design. It is especially useful for complex systems, such as microprocessors, ASICs, and other high-density circuits, ensuring better fault detection and improving the overall testability of the design. How Does Scan Work in VLSI? Scan involves converting sequential circuits into a