What’s New

Latest News

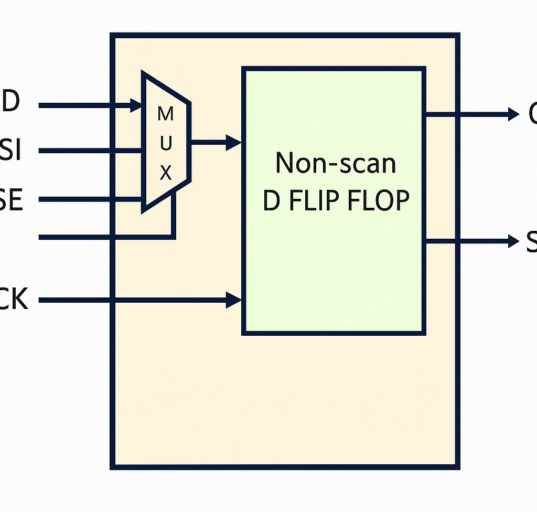

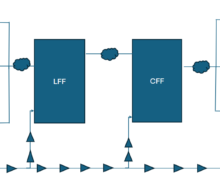

What is Scan in VLSI Design? Key Technique for Improved Testing

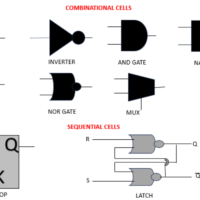

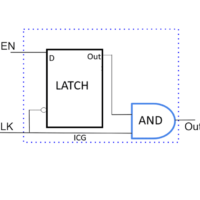

In VLSI (Very Large Scale Integration) design, scan is a technique used to facilitate testing and debugging of digital circuits by making it easier to observe and control.

- by Anuthipahal

- May 20, 2025

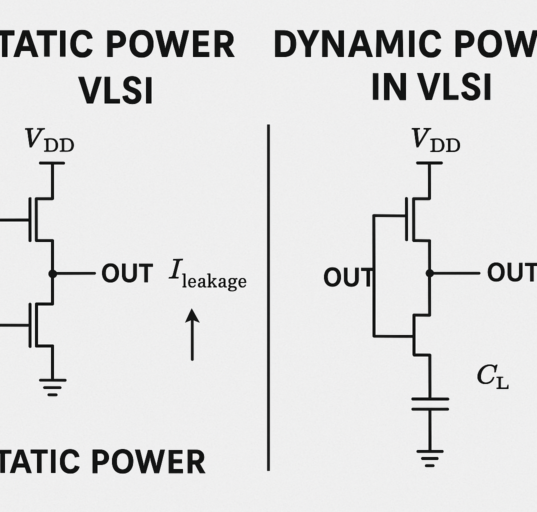

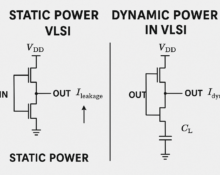

Static Power vs. Dynamic Power in VLSI: Key Differences and Significance

In VLSI (Very Large Scale Integration) design, understanding the distinction between static power and dynamic power is crucial for optimizing the performance and power efficiency of.

- by Anuthipahal

- May 12, 2025

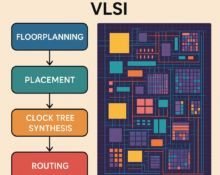

What is Physical Design in VLSI? A Key Process for Chip Fabrication

Physical design in VLSI (Very Large Scale Integration) refers to the process of converting a high-level logical design into a physical layout that can be fabricated on.

- by Anuthipahal

- May 9, 2025

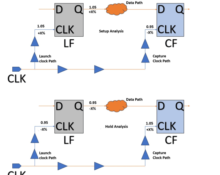

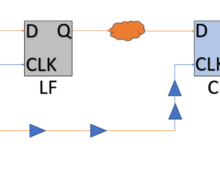

STATIC TIMING ANALYSIS [STA]: OCV vs AOCV vs POCV

In VLSI design, OCV (On-Chip Variation), AOCV (Advanced On-Chip Variation), and POCV (Process On-Chip Variation) refer to methods and models used for accounting for variations in.

- by Anuthipahal

- May 6, 2025

STATIC TIMING ANALYSIS [STA]: Optimization of Timing Violations in VLSI

Optimizing for timing violations in VLSI (Very-Large-Scale Integration) involves various strategies to ensure the chip operates within its specified timing requirements, particularly.

- by Anuthipahal

- May 5, 2025

Featured Post