Concept of Useful Skew

- Clock skewing is an intentional addition or removal of cell/net delays in the clock path to meet violating timing paths.

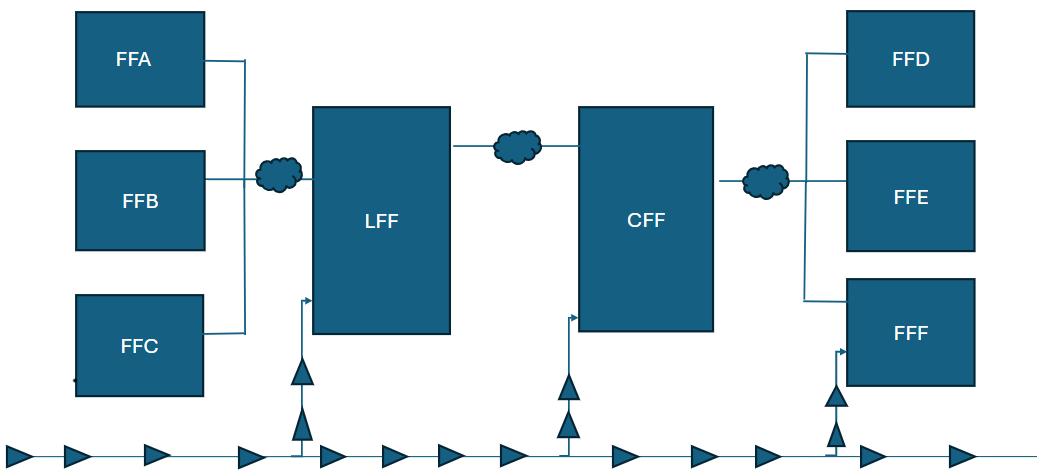

- For example, the timing path from LFF (Launch Flip Flop) to CFF (Capture Flip Flop) violates the setup.

- To fix this path, we can make some changes in the data path as well as the clock path. But we need to see the timing margin available in the previous/next paths to make any changes in the clock path so that the changes in the current path would not affect other paths’ timing.

We will first explore the fixes for setup violations, which involve only data path optimization:

- Upsizing the cells in the data path

- Vt swapping from Higher Vt flavors to lower Vt flavors to reduce data path delay [ HVT to LVT/ULVT or LVT to ULVT]

- Breaking long nets to address max transition violations and thus improve delays.

- Splitting the fan out of the driver cells.

- By addressing cross-talk delays by applying NDR rules and increasing spacing between aggressor and victim nets, and by increasing the width of victim nets.

- Reducing the Clock to Q delay of LFF (Launch flip flop).

- Replacing the CFF (Capture flip flop) with one that has a smaller setup time window to accommodate larger data path delays.

- Reducing library setup time for CFF by improving clock tran and data tran for its pins.

- Using higher metal layers with lower RC value in routing of the data path to reduce its delay.

Once we have exhausted data path optimization options, we will go for clock skewing as it involves touching of high fanout clock network.

Now, let us say, the timing path from LFF to CFF (refer to the given diagram) is violating hold.

- To fix this path, we can make some changes in the data path as well as the clock path. But we need to see the timing margin available in the previous/next paths to make any changes in the clock path so that the changes in the current path would not affect other paths’ timing.

We will first explore the fixes for hold violations, which involve only data path optimization –

- Inserting delay by inserting Buffers/Delay cells in the data path.

- Downsize data path cells.

- Using High threshold voltage cells (HVTs) in the data path or swapping LVT to HVT and ULVT to LVT/HVT cells.

- Increase routing length or use lower metal layers to increase data path delay.

- By addressing cross-talk delays by applying NDR rules and increasing spacing between aggressor and victim nets, and by increasing the width of victim nets.

- Reducing library hold time for CFF by improving clock tran and data tran for its pins.

Once we have exhausted data path optimization options, we will go for clock skewing as it involves touching of high fanout clock network.

Clock Push (Late Skew):

Clock push is a technique of adding delays in the clock path to meet/fix timing violations (setup/hold).

- Case –1 [Setup is violating]

- We can do a clock push,i.e., delaying the capture clock path.As we know, positive skew is good for setup and bad for hold. So, to fix the setup violation in the current path, we must add a delay by adding clock buffers/inverter pairs or downsizing buffers/inverter pairs in the capture clock path of the current timing path (LFF to CFF).

- It will improve the hold margin in the next path.

- But before going for this option, we need to make sure we have:

- Enough hold margin present in the current path (hold margin to the D* pins of CFF).

- Enough setup margin present in the next paths (setup from the CP pin of CFF).

As we are adding delay in the capture path, which is also a launch path for the next set of timing paths and it will degrade the setup violation there. And adding clock skew will degrade Hold for the timing paths ending at CFF.

- Case – 2 [Hold is violating]

- We can do a clock push in the launch clock path. As we know, positive skew is bad for hold. So, to fix hold in the current path, we can add buffers/inverter pairs or downsize buffers/inverter pairs in the launch clock path of the current timing path (LFF to CFF).

- It will improve the setup margin in the previous path.

- But before going for this option, we need to make sure we have:

- Enough setup margin present in the current path (setup from the CP pin of Launch Flip Flop LFF).

- Enough hold margin present in the previous path (hold margin to the D* pins of LFF).

As we are adding delay in the capture path of the previous timing path, it will degrade hold violation there due to additional skew. It will degrade the setup margin for all next paths as we are increasing the arrival time by adding a delay in the launch clock path.

Clock Pull (Early Skew):

In clock push, we are adding delay in the clock path, but here we will pull the clock, i.e., reduce the delay of the clock path, which will help us in meeting our timing in case the data path is fully optimized.

- Case –1 [Setup is violating]

- We can do a clock pull, i.e., early the launch clock path.

- As we know, positive skew is good for setup and bad for hold. So, to fix the setup violation in the current path, we can reduce delay by removing buffers/inverter pairs or upsizing buffers/inverter pairs or by bypassing the buffers/inverter pairs present in the launch clock path of the current timing path (LFF to CFF).

- It will improve the hold margin in the previous path.

- But before going for this option, we need to make sure we have:

- Enough hold margin present in the current path (hold margin from the CP pin of LFF)

- Enough setup margin present in the previous path (setup margin to the D* pins of LFF)

As we are reducing delay in the launch path, which is also a capture path for previous timing paths and it will degrade the setup violation there.

- Case – 2 (Hold is violating)

- We can do a clock pull in the capture clock path.

- As we know, positive skew is bad for hold. So, to fix hold in the current path, we can remove buffers/inverter pairs or upsize buffers/inverter pairs or bypass the buffers/inverter pairs present in the capture clock path of the current timing path (LFF to CFF).

- It will improve the setup margin in the next path.

- But before going for this option, we need to make sure we have:

- Enough setup margin present in the current path (setup margin to D* pins of CFF).

- Enough hold margin present in the next path (hold margin from the CP pin of CFF).

As we are reducing delay in the launch clock path of the next timing path, which will degrade the hold violation there.

Note – In clock push/pull techniques, while removing/adding or upsizing/downsizing buffers/inverter pairs, we must be cautious about clock tran violation which might pop up as a result of low drive strength clock cells being used for Clock skewing.

![Static Timing Analysis [STA]: Clock Skewing [Clock Push (Late Skew) and Clock Pull (Early Skew)]](https://anuthipahal.com/wp-content/themes/neeon/assets/img/noimage.jpg)

Leave feedback about this